Figure 1 from Measurement on snapback holding voltage of high-voltage LDMOS for latch-up consideration | Semantic Scholar

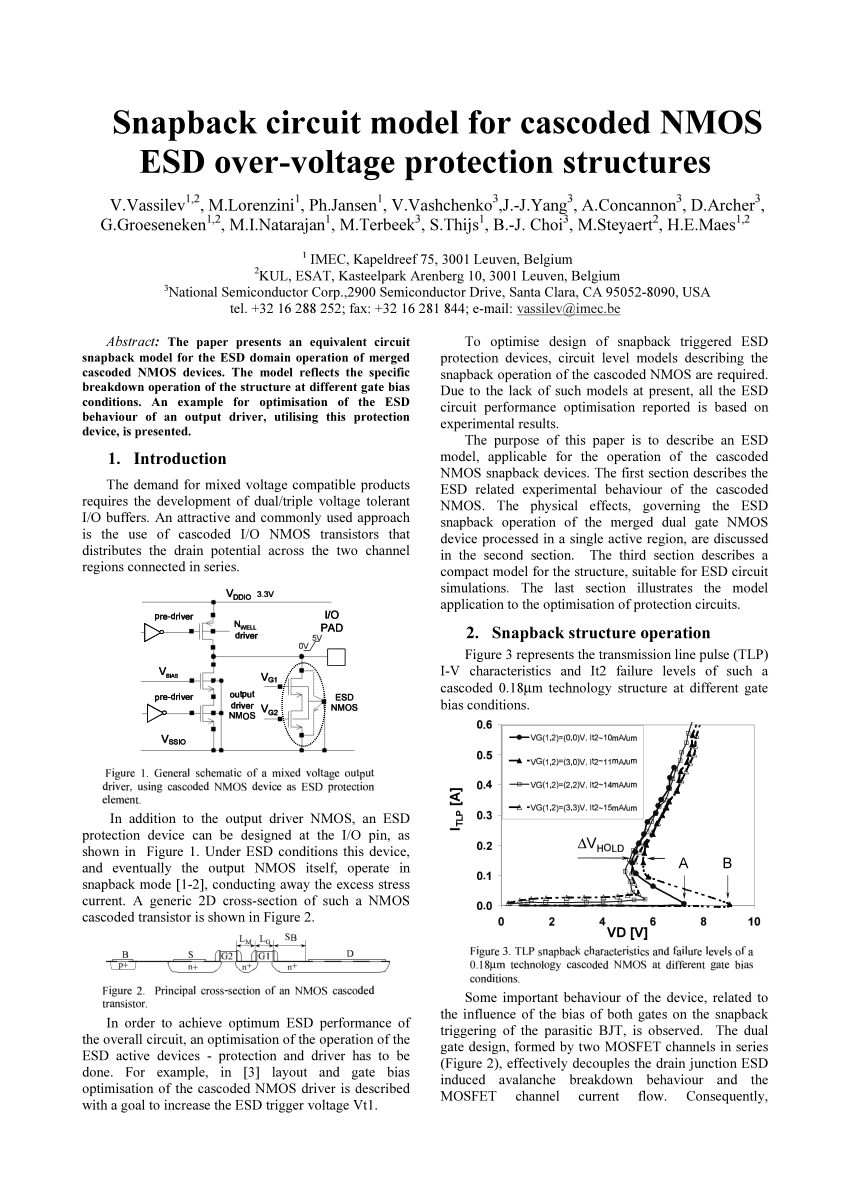

Modeling MOS snapback and parasitic bipolar action for circuit-level ESD and high current simulations | Semantic Scholar

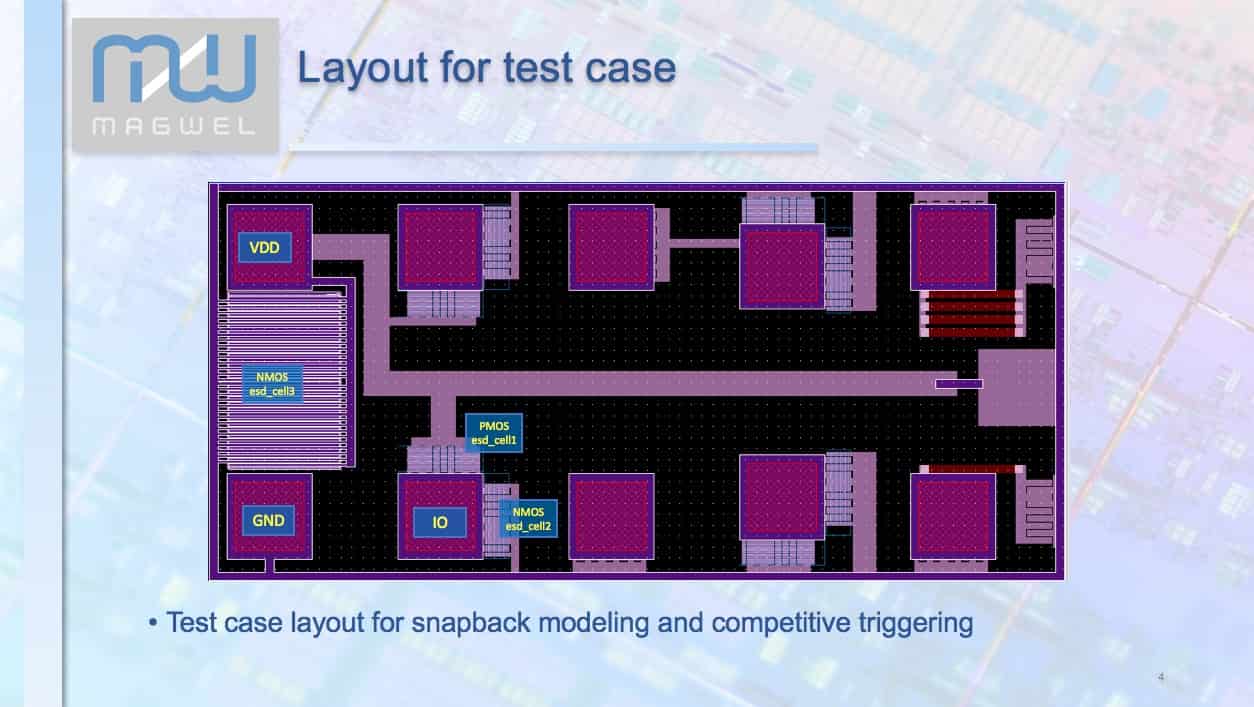

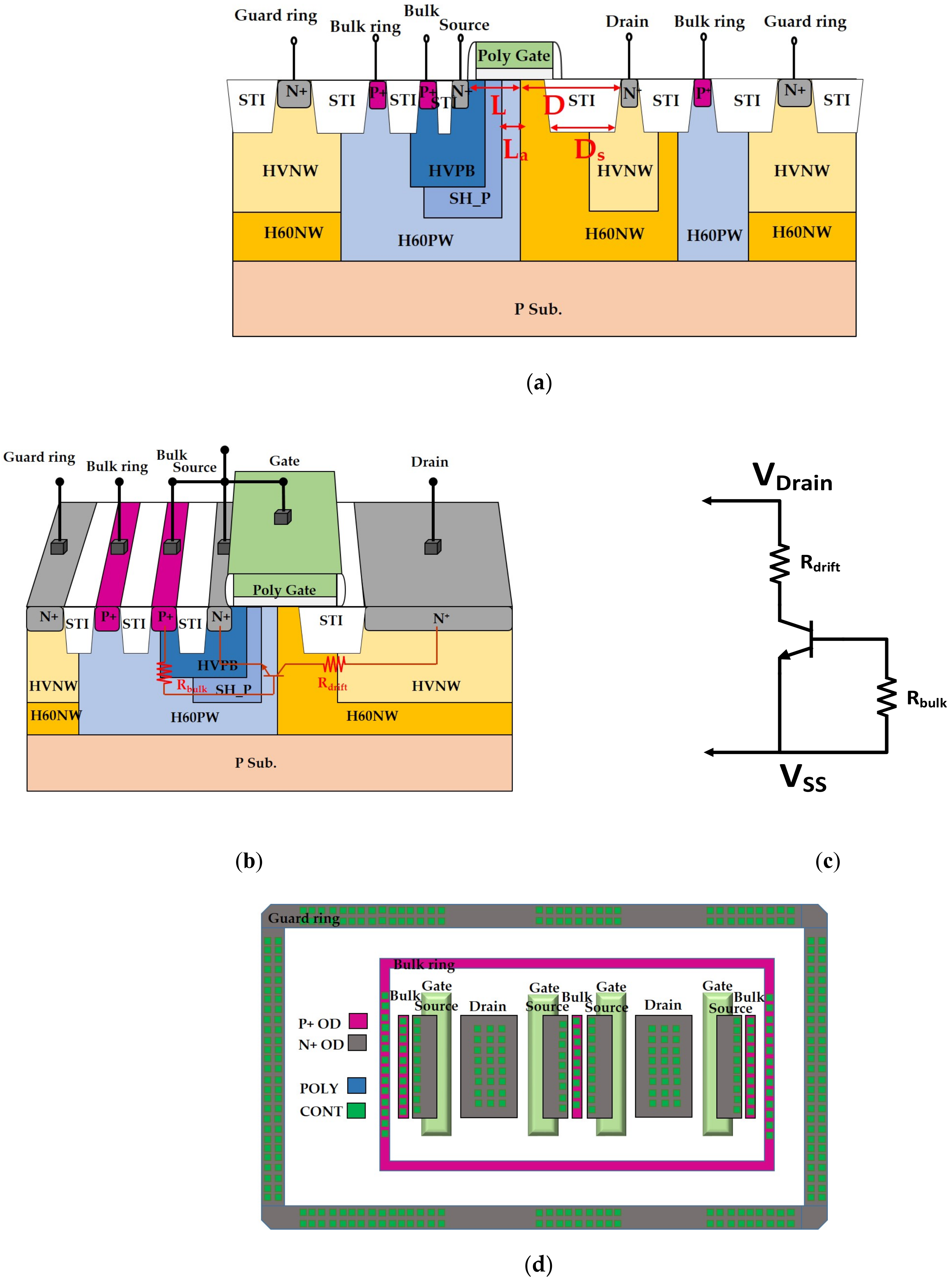

Electronics | Free Full-Text | Layout Strengthening the ESD Performance for High-Voltage N-Channel Lateral Diffused MOSFETs

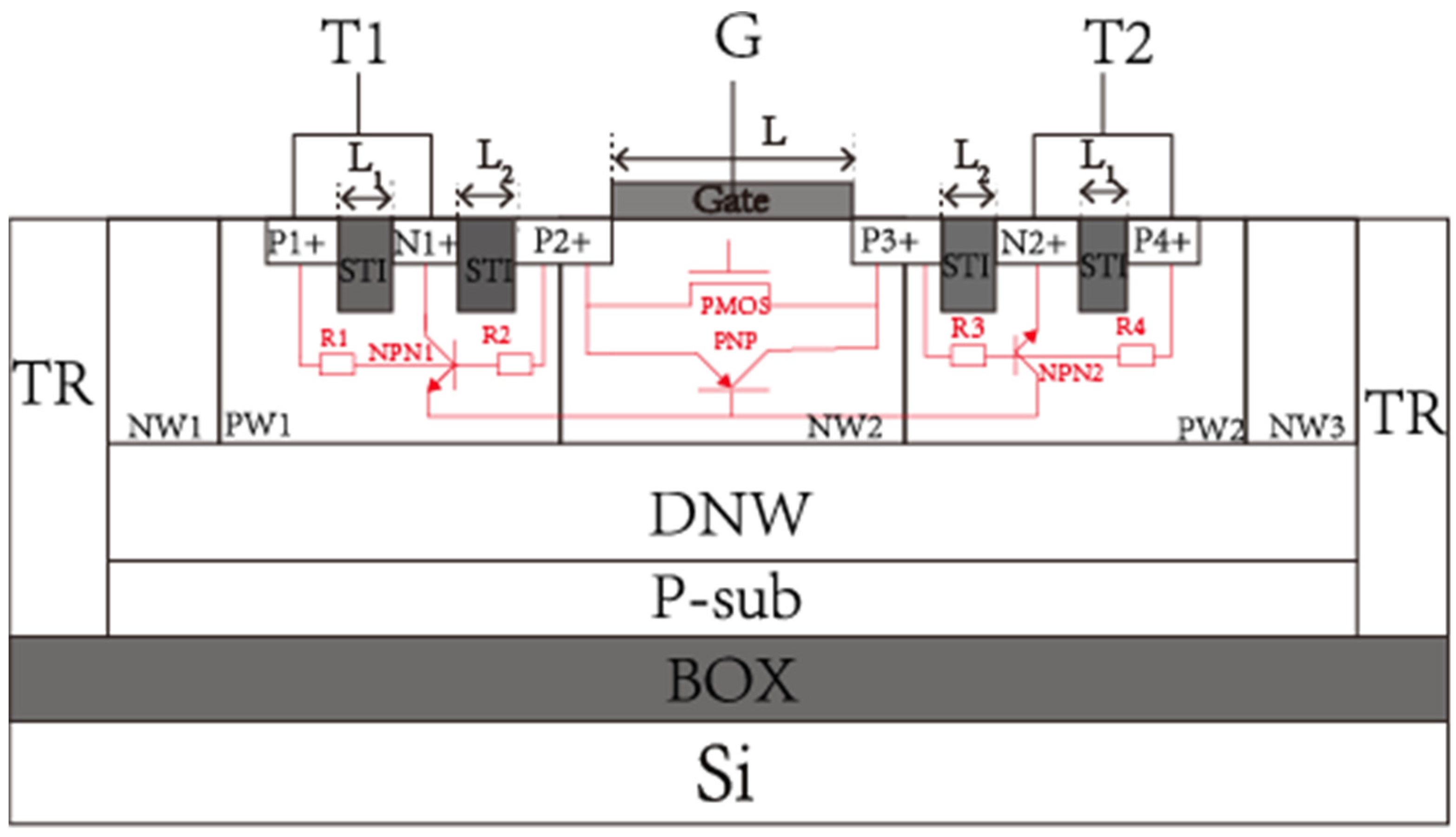

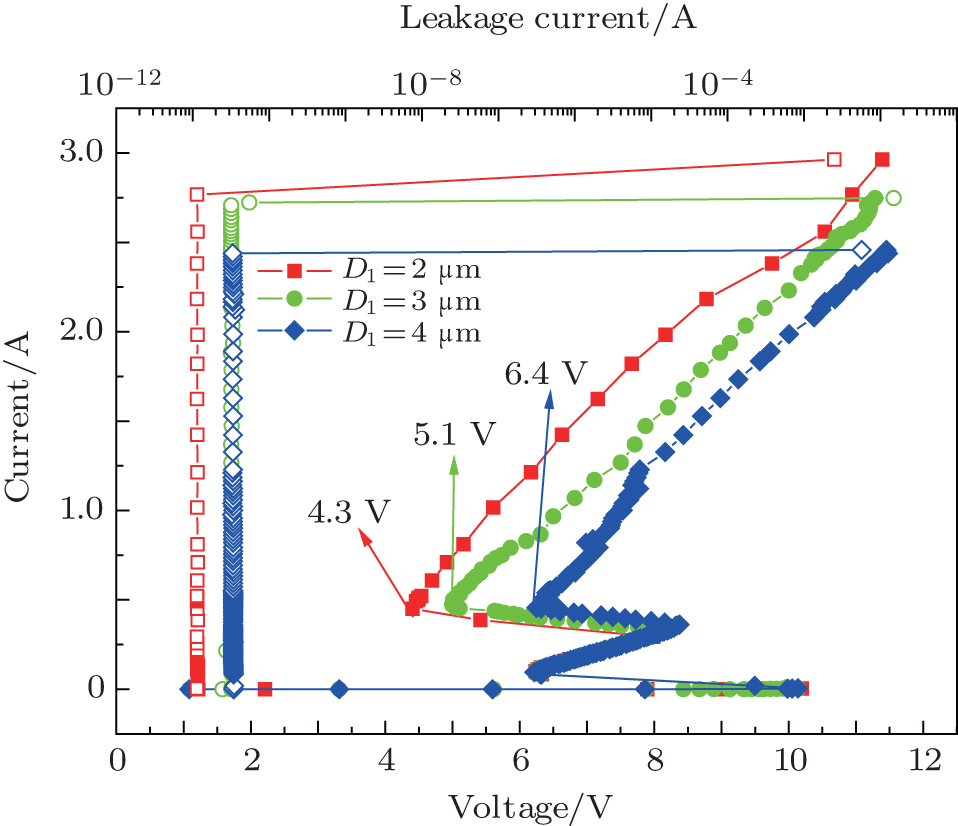

Electronics | Free Full-Text | The ESD Characteristics of a pMOS-Triggered Bidirectional SCR in SOI BCD Technology

PDF) Modeling snapback of LVTSCR devices for ESD circuit simulation using advanced BJT and MOS models | Yuanzhong Zhou - Academia.edu

Bipolar effects in snapback mechanism in advanced n-FET transistors under high current stress conditions